您的购物车目前是空的!

标签: B205mini

-

B200/B210/B200mini/B205mini(硬件资源)

设备概述

USRP 总线系列提供完全集成的单板通用软件无线电外设平台,连续频率覆盖范围为 70 MHz 至 6 GHz。它专为低成本实验而设计,集成了高达 56MHz 实时带宽的完全集成直接变频收发器、开放且可重新编程的 Spartan6 FPGA,以及快速便捷的总线供电超高速 USB 3.0 连接。

主要特点

B200

- Xilinx Spartan 6 XC6SLX75 FPGA

- Analog Devices AD9364 RFIC 直接转换收发器

- 频率范围:70 MHz – 6 GHz

- 最大瞬时带宽:56 MHz

- 全双工,SISO(1 Tx 和 1 Rx)

- 快速便捷的总线供电 USB 3.0 连接

- 可选板载 GPSDO

B210

- Xilinx Spartan 6 XC6SLX150 FPGA

- Analog Devices AD9361 RFIC 直接转换收发器

- 频率范围:70 MHz – 6 GHz

- 最大瞬时带宽:56 MHz(61.44MS/s 正交)

- 全双工,MIMO(2 Tx 和 2 Rx)

- 快速便捷的总线供电 USB 3.0 连接

- 可选板载 GPSDO

B200mini

- Xilinx Spartan-6 XC6SLX75 FPGA

- Analog Devices AD9364 RFIC 直接转换收发器

- 频率范围:70 MHz – 6 GHz

- 最大瞬时带宽:56 MHz

- 全双工,SISO(1 Tx 和 1 Rx)

- 快速便捷的总线供电 USB 3.0 连接

B200mini-i

- 工业级 Xilinx Spartan-6 XC6SLX75 FPGA

- Analog Devices AD9364 RFIC 直接转换收发器

- 频率范围:70 MHz – 6 GHz

- 最大瞬时带宽:56 MHz

- 全双工,SISO(1 Tx 和 1 Rx)

- 快速便捷的总线供电 USB 3.0 连接

B205mini-i

- 工业级 Xilinx Spartan-6 XC6SLX150 FPGA

- Analog Devices AD9364 RFIC 直接转换收发器

- 频率范围:70 MHz – 6 GHz

- 最大瞬时带宽:56 MHz

- 全双工,SISO(1 Tx 和 1 Rx)

- 快速便捷的总线供电 USB 3.0 连接

前端规格

调谐

射频前端具有独立可调的接收和发射链路。在 B200 和 B200 mini 上,只有一个发射和一个接收射频前端。在 B210 上,发射和接收都可以在 MIMO 配置中使用。仅在 B210 的 MIMO 情况下,两个接收前端共享 RX LO,两个发射前端共享 TX LO。每个 LO 可独立调谐,频率范围为 50 MHz 到 6 GHz,并且可以与 1 个或 2 个通道一起使用;所有使用相同 LO 的通道必须使用相同的采样参数,包括采样率和射频中心频率。

增益

所有前端都有单独的模拟增益控制。接收前端的可用增益为 76 dB;发射前端的可用增益为 89.8 dB。增益设置是应用特定的,但建议用户考虑使用至少一半的可用增益,以获得合理的动态范围。

带宽

模拟前端的带宽可在 200 kHz 到 56 MHz 之间无缝调节。

通常,在请求任何可能的主时钟频率时,UHD 会自动配置模拟滤波器,以避免任何混叠(RX)或带外发射,同时允许尽可能干净的信号通过。

然而,如果您恰好在 RX LO 频率的主时钟频率的一半范围内遇到非常强的干扰信号,您可能需要减少此模拟带宽。您可以通过调用

uhd::usrp::multi_usrp::set_rx_bandwidth(bw)来实现。控制模拟 RX 带宽的属性是

bandwidth/value。UHD 不允许您设置超过当前主时钟频率的带宽。

射频规格

USRP B200/B210/B200mini/B205mini 基于 Analog Devices AD936x 集成收发器芯片,设备的整体射频性能在很大程度上由收发器芯片本身决定。

射频性能

- 单边带/本振(SSB/LO)抑制:-35/50 dBc

- 相位噪声 3 GHz:1.0 度 RMS

- 相位噪声 6 GHz:1.5 度 RMS

- 输出功率:>10 dBm

- 输入第三阶截断点(IIP3)(典型噪声系数下):-20 dBm

- 典型噪声系数:<8 dB

- 最大输入功率:-15 dBm

输入/输出阻抗

所有射频端口与 50 欧姆匹配,返回损耗通常为 -10 dB 或更好。详细测试待定。

输入功率等级

B200/B210/B200mini/B205mini 的最大输入功率为 -15 dBm。

射频性能数据

B200mini / B205mini

B200 / B210

硬件规格

- B200

- 当前硬件版本:6

- 所需最小 UHD 版本:3.8.4

- B200 Rev 5(基于 AD9364 的板卡)需要最小 UHD 版本 3.8.4

- B210

- 当前硬件版本:5

- 所需最小 UHD 版本:3.6.0

- B200mini

- 当前硬件版本:2

- 所需最小 UHD 版本:3.9.0

- B200mini-i

- 当前硬件版本:2

- 所需最小 UHD 版本:3.9.0

- B205mini-i

- 当前硬件版本:1

- 所需最小 UHD 版本:3.9.2

物理规格

尺寸

- B200mini/B205mini:5.0 x 8.4 cm

- B200/B210:9.7 x 15.5 x 1.5 cm

重量

- B200mini:24.0 g

- B200/B210:350 g

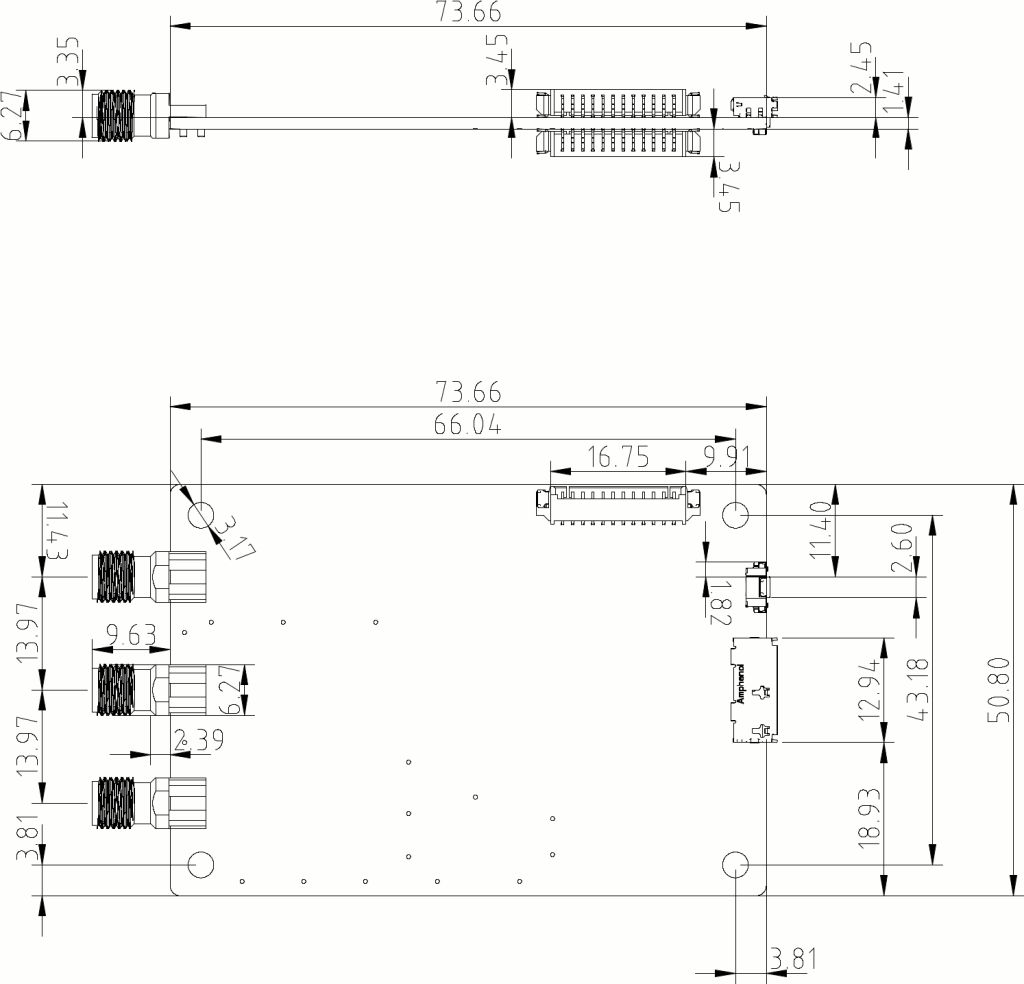

机械图纸

B200mini

B200

B210

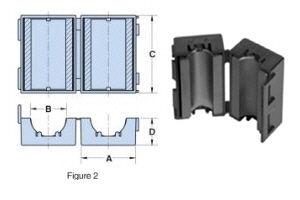

B200/B210外壳

CAD/STP 模型

B200mini

B20xmini-i

B200

B210

B200/B210 外壳

环境规格

- 工作温度范围

- B200 / B210:25 °C

- B200mini – 仅主板:0 – 40 °C

- B200mini – 含外壳:-20 – 60°C

- B200mini-i / B205mini-i – 仅主板:0 – 45 °C

- B200mini-i / B205mini-i – 含I级外壳:-40 – 75°C

- 工作湿度范围

- 10% 至 90% 无凝露

原理图

B200mini/B200mini-i/B205mini-i

B200/B210

关键组件数据表

零件编号 描述 原理图 ID (Page) Mini-Circuits TCM1-63AX+ Transformer T1 (1,3); T2 (1,3) Analog Devices AD9364 RF Transceiver U1 (2) Analog Devices AD9361 RF Transceiver U2 (2,8) AD9361/AD9364 Product Page RF Transceiver – Xilinx Spartan-6 Product Page FPGA U1 (2,3,4,6); PG1 (6); U18B, U18C (7); U18D (8); U18E, U18F (9); U18G, U18H (10) XC6SLX75 / XC6SLX150 FPGA ADF4001 Frequency Synthesizer U101 (1) CYUSB3014 FX3: SuperSpeed USB Controller U3 (5,6); U13 (5) EZ-USB FX3™ Product Page SKY13317 Antenna Switch U801, U810 (8) BD3150L50100A00 Balun U802, U808, U809, U815 (8) PGA−102+ Amplifier U804, U817 (8) VCTCXO VCTCXO (B200mini only) – 525L20DA40M0000 VCTCXO (B200/B210 only) X100 (1) Jackson Labs LC_XO Spec Sheet Manual Optional GPSDO (B200/B210 only) U100 (1) 外壳

SMA 连接器应拧紧至 4 英寸磅。

B200mini

B200mini C级机箱

B200mini I级机箱

B205mini

B205mini I级外壳

B200/B210

- 全钢外壳

- 兼容绿色 USRP B200 和 B210 设备(版本 6 或更高版本)

- 前后 K 型插槽,提供防盗保护

FPGA

利用率统计数据可能会因 UHD 版本不同而有所变化。此信息截至 UHD 3.9.4 版本为准。

B200

Device utilization summary: --------------------------- Selected Device : 6slx75fgg484-3 Slice Logic Utilization: Number of Slice Registers: 15781 out of 93296 16% Number of Slice LUTs: 19987 out of 46648 42% Number used as Logic: 15983 out of 46648 34% Number used as Memory: 4004 out of 11072 36% Number used as RAM: 972 Number used as SRL: 3032 Slice Logic Distribution: Number of LUT Flip Flop pairs used: 24062 Number with an unused Flip Flop: 8281 out of 24062 34% Number with an unused LUT: 4075 out of 24062 16% Number of fully used LUT-FF pairs: 11706 out of 24062 48% Number of unique control sets: 434 IO Utilization: Number of IOs: 172 Number of bonded IOBs: 155 out of 280 55% IOB Flip Flops/Latches: 124 Specific Feature Utilization: Number of Block RAM/FIFO: 144 out of 172 83% Number using Block RAM only: 144 Number of BUFG/BUFGCTRLs: 4 out of 16 25% Number of DSP48A1s: 76 out of 132 57%B210

Device utilization summary: --------------------------- Selected Device : 6slx150fgg484-3 Slice Logic Utilization: Number of Slice Registers: 29310 out of 184304 15% Number of Slice LUTs: 36486 out of 92152 39% Number used as Logic: 29279 out of 92152 31% Number used as Memory: 7207 out of 21680 33% Number used as RAM: 1752 Number used as SRL: 5455 Slice Logic Distribution: Number of LUT Flip Flop pairs used: 43635 Number with an unused Flip Flop: 14325 out of 43635 32% Number with an unused LUT: 7149 out of 43635 16% Number of fully used LUT-FF pairs: 22161 out of 43635 50% Number of unique control sets: 723 IO Utilization: Number of IOs: 180 Number of bonded IOBs: 163 out of 338 48% IOB Flip Flops/Latches: 148 Specific Feature Utilization: Number of Block RAM/FIFO: 186 out of 268 69% Number using Block RAM only: 186 Number of BUFG/BUFGCTRLs: 4 out of 16 25% Number of DSP48A1s: 152 out of 180 84%B200mini

Device utilization summary: --------------------------- Selected Device : 6slx75csg484-3 Slice Logic Utilization: Number of Slice Registers: 15949 out of 93296 17% Number of Slice LUTs: 19963 out of 46648 42% Number used as Logic: 16140 out of 46648 34% Number used as Memory: 3823 out of 11072 34% Number used as RAM: 972 Number used as SRL: 2851 Slice Logic Distribution: Number of LUT Flip Flop pairs used: 23859 Number with an unused Flip Flop: 7910 out of 23859 33% Number with an unused LUT: 3896 out of 23859 16% Number of fully used LUT-FF pairs: 12053 out of 23859 50% Number of unique control sets: 429 IO Utilization: Number of IOs: 123 Number of bonded IOBs: 114 out of 328 34% IOB Flip Flops/Latches: 147 Specific Feature Utilization: Number of Block RAM/FIFO: 110 out of 172 63% Number using Block RAM only: 110 Number of BUFG/BUFGCTRLs: 6 out of 16 37% Number of DSP48A1s: 76 out of 132 57% Number of PLL_ADVs: 1 out of 6 16%B205mini

Device utilization summary: --------------------------- Selected Device : 6slx150csg484-3 Slice Logic Utilization: Number of Slice Registers: 15949 out of 184304 8% Number of Slice LUTs: 19963 out of 92152 21% Number used as Logic: 16140 out of 92152 17% Number used as Memory: 3823 out of 21680 17% Number used as RAM: 972 Number used as SRL: 2851 Slice Logic Distribution: Number of LUT Flip Flop pairs used: 23859 Number with an unused Flip Flop: 7910 out of 23859 33% Number with an unused LUT: 3896 out of 23859 16% Number of fully used LUT-FF pairs: 12053 out of 23859 50% Number of unique control sets: 429 IO Utilization: Number of IOs: 123 Number of bonded IOBs: 114 out of 338 33% IOB Flip Flops/Latches: 147 Specific Feature Utilization: Number of Block RAM/FIFO: 110 out of 268 41% Number using Block RAM only: 110 Number of BUFG/BUFGCTRLs: 6 out of 16 37% Number of DSP48A1s: 76 out of 180 42% Number of PLL_ADVs: 1 out of 6 16%接口和连接

B200/B210/B200mini – USB 3.0

GPIO

上电状态

硬件的上电状态和前面板 GPIO 的 UHD 初始状态为高阻(high-Z)。对于 B2xx 和 B2xxmini,GPIO 引脚没有外部拉高/拉低电阻,但 FPGA 内部有,并且配置如下:- B2xx:拉高

- B2xxmini:拉高

输出电流

GPIO 被配置为 LVCMOS33 输出,并且 B2xx 上有拉高电阻。对于 Spartan 6,LVCMOS 和 LVTTL 的驱动强度为 12 mA,除非另有说明。时钟参考输入

- B200mini/B200mini-i/B205mini-i

- 1-PPS 或 10 MHz 输入

- 1-PPS

- 最大:-5V / +5V

- 最小:0V / +2.5V

- 10 MHz

- 最大:0V / +5V

- 最小:0V / +1.8V

或

- +10dBm ~ +27dBm

- 1-PPS

- 1-PPS 或 10 MHz 输入

- B200/B210

- 1-PPS

- 最大:5V

- 10 MHz

- 最大:15dBm(3.5Vpp,50 欧姆负载)

- 1-PPS

认证

- RoHS:自2010年12月1日起,除非另有说明,所有Ettus Research产品均符合RoHS标准。

- 中国RoHS:《电子信息产品污染控制管理办法》

- 中国客户:遵守中国《电子信息产品有害物质限制使用指令》(RoHS) 的规定。

- 欧盟认证:为确保符合欧盟无线电设备认证,如使用 GPIO 线缆,应将铁氧体磁珠(包含在 NI 部件号 785825-01 和 785826-01 的套件中)固定到线缆上。具体操作如下:打开卡扣式铁氧体磁珠,将其包裹在 GPIO 线缆上。

常见疑问解答

这是关于 USRP B200/B210/B200mini 的常见问题列表。如果您有本文档未解答的问题,请联系我们:xudong.zhao@tekdf.com 。

USRP B200/B210 能兼容 USB 2.0 吗?

可以。如果没有 USB 3.0 端口,USRP B200 和 USRP B210 都会降级到 USB 2.0 标准。需要考虑以下几点。首先,USB 2.0 的数据速率较慢。根据 USB 控制器、操作系统和其他因素,USB 2.0 的采样率最高可达 8 MS/s。此外,在 USB 2.0 模式下,您可能无法为 USRP B200/B210 进行总线供电。

USB 3.0 的采样率应该是多少?USB 2.0 呢?

USB 3.0 的性能和吞吐量会因主机控制器而异。我们建议使用英特尔 7、8 和 9 系列 USB 控制器。在 Linux 系统中,lspci 命令将显示系统上的 USB 控制器。

我什么时候可以通过 USB 为 USRP B200/B210/B200mini 供电?

不同的控制器使用体验会有所不同。一般来说,总线供电是 SISO 操作的理想选择。如果您使用 USRP B210 的两个通道,我们建议使用外部电源。我们出售适用于各种 USRP 的外部电源。

当 USRP B210 使用总线供电时,不建议使用 MIMO 进行 MIMO 操作。如果安装了 GPS 校准的振荡器,也不建议使用总线供电运行 B210。

USRP 的功耗是多少?

下表显示了使用 6V 电源供电的 USRP B210 的功耗(瓦)。使用 5V 电源(USB 供电)或 USRP B200 时,功耗会略低。表中显示的采样率是 USB 3.0 接口上的总采样率。

类型 5 Msps 15.36 Msps 30.72 Msps 56 Msps 61.44 Msps 1 RX 1.92 2.112 2.184 2.508 2 RX 2.148 2.436 2.508 2.64 1 TX 2.184 2.34 2.352 2.22 2 TX 2.76 2.88 2.904 2.64 Full Duplex (1×1) 2.508 2.736 2.796 3.168 2×2 MIMO 3.252 3.588 3.672 4.11 4.092 可以使用 USRP B200/B210 构建多设备系统吗?

可以使用 10 MHz/1 PPS 输入和类似 OctoClock-G 的外部分配系统同步多个 USRP B200/B210 设备。但是,当多个设备通过同一控制器进行数据流传输时,USB 3.0/2.0 的性能会有很大差异。通常,如果您需要构建高通道数系统,我们建议使用 USRP N200/N210。

可以访问 USRP B200/B210 的源代码吗?

可以。USRP B200/B210 由 USRP Hardware DriverTM 软件支持。您可以在 UHD git 仓库中找到 USRP B200/B210 以及所有其他 USRP 型号的驱动程序和 FPGA 源代码:

http://files.ettus.com/manual/page_build_guide.html

USRP B200/B210 支持哪些操作系统?

USRP B200/B210 支持 Linux、OSX (MacOSX / macOS) 和 Windows 系统。

USRP B200/B210 可以与 GNU Radio 兼容吗?

可以。USRP B200/B210 可以与我们的 GNU Radio 插件 gr-uhd 兼容。

USRP B200/B210 可以与 MATLAB 和 Simulink 兼容吗?

可以。您需要安装 Communications System Toolbox Support Package for USRP Radio。

USRP B200/B210 可以与 OpenBTS 兼容吗?

可以。这是一个第三方应用程序,您可以在此处找到说明:OpenBTS – 构建、安装、运行。

我需要哪些工具来编程 FPGA?

USRP B200 和 USRP B210 分别包含 Spartan 6 XC6SLX75 和 XC6S150。USRP B200 可以使用 Xilinx 的免费版工具进行编程,而 USRP B210 上更大的 FPGA 则需要许可证。

可以将 GPSDO 与 USRP B200/B210 一起使用吗?

我们提供板载 GPS 校准 OCXO 和板载 GPS 校准 TCXO,它们与 USRP B200/B210 兼容。它们提供高精度 XO,可根据全球 GPS 标准进行校准。请注意:当 GPSDO OCXO 型号集成在 USRP B200/B210 上时,设备应使用外部电源供电,而不是 USB 总线供电。TCXO 版本可以通过 USB 总线供电。

-

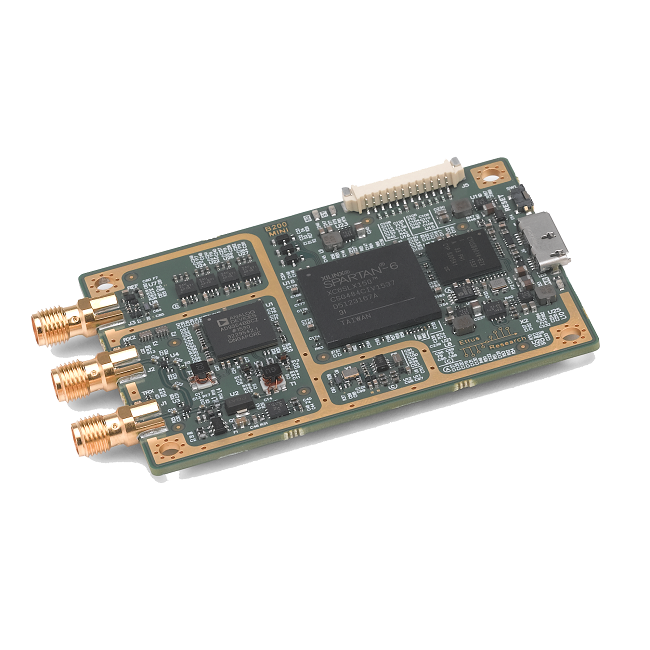

USRP B205mini

简介

70 MHz~6 GHz,1通道USRP软件无线电设备,仅信用卡大小。

USRP‑B205mini是一款信用卡大小的并采用全双工运行的可调谐RF收发器。 它提供了基于USB 3.0的总线供电连接,还包括用于 GPIO、JTAG 和与 10 MHz 时钟参考或 PPS 时间参考输入信号同步的连接器。

NI USRP‑B205mini还可以用于以下通信应用:白色空间; 广播FM; 公共安全; 陆地移动,低功率非授权设备(ISM)频段; 传感器网络; 业余无线电或GPS。

发射指标

1 频率范围(Frequency range) 70 MHz to 6 GHz 2 频率步进(Frequency step) <1 kHz 3 最大输出功率(Maximum output power) > 10 dBm 4 增益范围(Gain range) 89.75 dB 5 增益步进(Gain step) 0.25 dB 6 频率稳定度(Frequency accuracy) ± 2 ppm 7 最大瞬时实时带宽(Maximum instantaneous real-time bandwidth) 12-bit 56 MHz 8 最大IQ速率(Maximum I/Q sample rate) 连续流 15 MS/s 突发模式单通道 61.44 MS/s 9 DAC性能(Digital-to-analog converter) DAC位宽 12bit 10 通道数(Number of channels) 2 接收指标

1 频率范围(Frequency range) 70 MHz to 6 GHz 2 频率步进(Frequency step) <1 kHz 3 增益范围(Gain range) 76 dB 4 增益步进(Gain step) 1.0 dB 最大输入功率(Maximum input power) -15 dBm 噪声系数(Noise figure) < 8 dB 5 频率稳定度(Frequency accuracy) ± 2 ppm 6 最大瞬时实时带宽(Maximum instantaneous real-time bandwidth) 56 MHz 7 最大IQ速率(Maximum I/Q sample rate) 连续波 15 MS/s 突发模式单通道 61.44 MS/s 8 ADC性能(Analog-to-digital converter) DAC位宽 12bit 9 通道数(Number of channels) 2 功率

1 平均功率 12 W to 15 W 2 最大功率 18 W 3 电源输入 DC:5 V 物理尺寸

1 长宽高 8.33 cm × 5.08 cm × 0.84 cm 2 重量 24 g 报价单

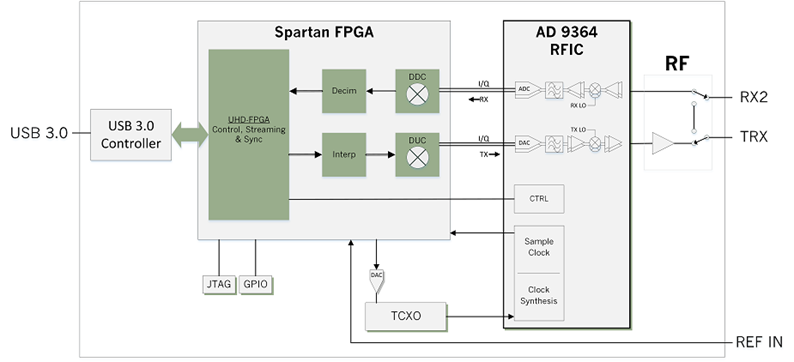

序号 厂家 税前 税后(13%) 开票 货期 1 NI 12,410 14,023.3 专票 1月 系统框图

接收路径:

- 低噪声放大器和驱动放大器放大输入的信号。

- 锁相环 (PLL) 控制压控振荡器 (VCO),以便设备时钟和本地振荡器 (LO) 可以将频率锁定到参考信号。

- 混频器将信号下变频为基带同相 (I) 和正交相位 (Q) 分量。

- 带通滤波器可降低信号中的噪声和高频成分。

- 模数转换器 (ADC) 将 I 和 Q 数据数字化。

- 数字下变频器 (DDC) 将信号混合、滤波并抽取至用户指定的速率。

- 下变频后的样本通过USB 3.0或USB 2.0连接 传递到主机。

传输路径:

- 主机合成基带 I/Q 信号并通过USB 3.0或USB 2.0连接将信号传输到设备。

- 数字上变频器 (DUC) 将信号混合、滤波和内插至61.44 MS/s。

- 数模转换器 (DAC) 将信号转换为模拟信号。

- 带通滤波器可降低信号中的噪声和高频成分。

- 混频器将信号上变频至用户指定的射频频率。

- PLL 控制 VCO,以便设备时钟和 LO 能够频率锁定到参考信号。

- 发射放大器将信号放大并通过天线发射。

欢迎您联系

东枫科技:赵旭栋