您的购物车目前是空的!

标签: USRP

-

TwinRX 10-6000 MHz 2 Rx (80 MHz, X Series only)

784097-01 | TwinRX USRP Daughterboard (10 MHz – 6 GHz, 80 MHz BW, 2 RX) $ 5,260.00 USD

The TwinRX daughterboard for the USRP™ X Series software-defined radios is a dual-channel superheterodyne receiver that offers wide dynamic range and accurate phase synchronization with LO sharing for spectrum monitoring and direction-finding applications.

Overview

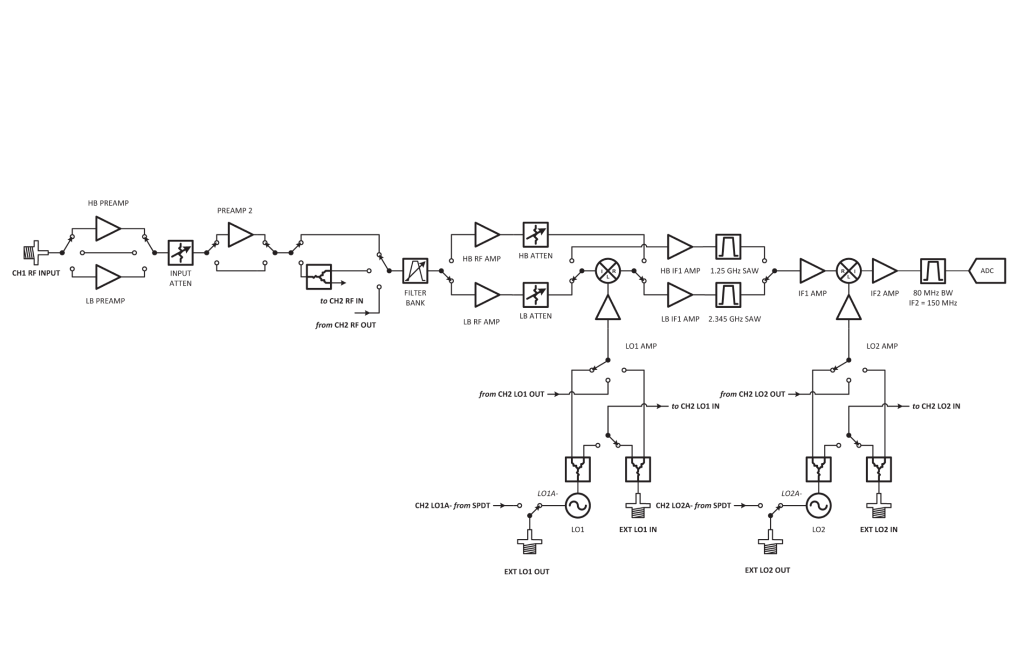

The TwinRX daughterboard for the USRP™ X Series software defined radios is a dual channel superheterodyne receiver that offers wide dynamic range and accurate phase synchronization for spectrum monitoring and direction finding applications. The RF signal chain features preampilifiers, preselectors, attenuators, and two mixer stages for excellent selectivity and spurious performance. The receiver is tunable from 10 MHz – 6 GHz and has 80 MHz of instantaneous bandwidth per channel, providing the versatility necessary to analyze a variety of signals in multiple bands of interest. Users can tune the two channels independently to simultaneously monitor uplink and downlink communication with a combined bandwidth of 160 MHz. The ability to share the LO between channels across multiple daughterboards enables the phase-aligned operation required to implement scalable multichannel phased arrays. The receiver is capable of fast frequency hopping to detect frequency agile emitters. The USRP Hardware Driver™ (UHD) software API automatically configures RF attenuation and preamplication to optimize dynamic range in favor of noise figure for faint signals, or IP3 for stronger signals. With the RF Network on Chip (RFNoC™) FPGA development framework, users can seamlessly off load compute intensive components of their application from host to FPGA for hardware acceleration and real-time performance.

Features

- Frequency range: 10 MHz – 6 GHz

- Bandwidth: 80 MHz per channel

- Channels: Two-stage superheterodyne, 2 RX, Independent tuning

- LO sharing

- USRP compatibility: X Series

- RF shielding

- Coherent and phased aligned operation

Block Diagram

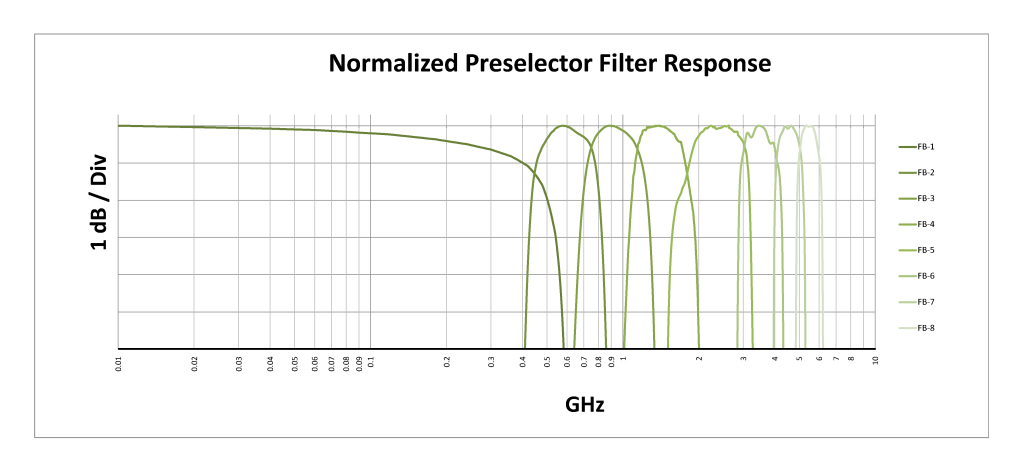

RF Information

Additional Resources

Kit Contents

- TwinRX Daughterboard

- Screw Kit

- 2x LO Sharing Cables

- 2x Front Panel Cables

- 2x Front Panel Washers and Bolts

- Hardware Installation Guide

- Getting Started Guide

Quotes and Sales

Email:sales@tekdf.com

Wechat:dftech_info

-

USRP-2974

785606-01 | USRP-2974 High Performance Embedded SDR, 10 MHz-6 GHz, 160 MHz bandwidth $ 25,703.00 USD

Provides deterministic control of transceivers using an onboard FPGA and processor for rapidly prototyping high-performance wireless communications systems.

Overview

The USRP Software Defined Radio Stand-Alone Device built with an FPGA and an Intel i7 onboard processor which you can provision with NI Linux Real-Time, Linux Fedora, or Linux Ubuntu Real-Time Operating Systems. You can program the onboard processor and FPGA with LabVIEW Communications System Design Suite or use an open-source software workflow to deterministically control your application.

The USRP-2974 is ideal for prototyping a range of advanced research applications that include stand-alone LTE or 802.11 device emulation; Medium Access Control (MAC) algorithm development; multiple input, multiple output (MIMO) systems; heterogeneous networks; LTE relaying; RF compressive sampling; spectrum sensing; cognitive radio; beamforming; and direction finding.

- Stand-alone (embedded) or host-based (network streaming) operation

Features

FPGA

- Xilinx Kintex-7 410T

- 14 bit ADC, 16 bit DAC

- Gen1x4 PCIe Connection

- SFP+ High Speed Serial Link

On-board Processor

- x86 onboard processor equipped with NI Linux Real Time OS for deterministic processing

- Intel Core i7 2 GHz Quad Core Processor

- Congatec COM Express Conga-TS170 SoM

- 8 GB DDR4

- MicroUSB to the SoM

- RJ45 (1 GbE)

- PCIe Gen x4

RF

- 2 RX, 2TX

- 10 MHz to 6 GHz extended frequency range

- Up to 160 MHz of instantaneous bandwidth per channel

- RX, TX filter bank

- GPS-Disciplined OCXO

- Clock reference

- PPS time reference

- External RX, TX LO input ports

- Built-in GPSDO

- Interface I/O

Interface I/O

- Two USB 3.0 ports

- Two USB 2.0 ports

- USB 1.0 JTAG

- Display Port

- AUX I/O

- Two SFP+ ports (1 Gigabit Ethernet, 10 Gigabit Ethernet, Aurora)

- PCIe Gen x4

- 1 Gb Ethernet (connection to host)

- Ref In/Out

- PPS In/Out

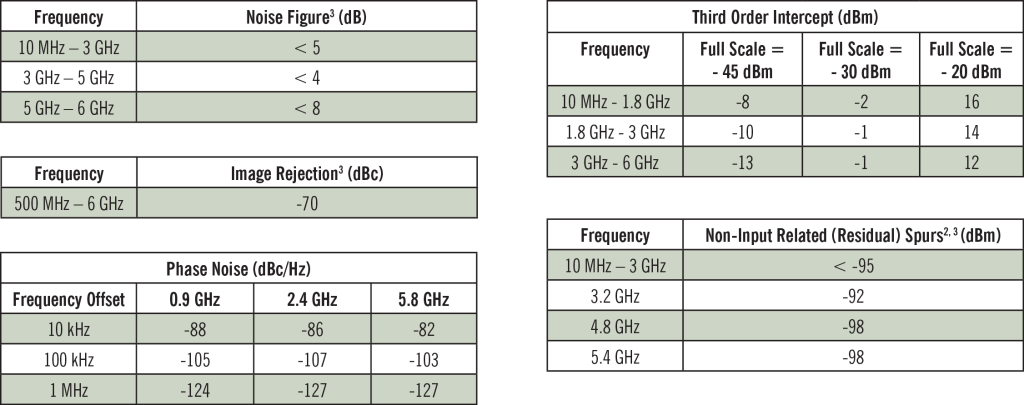

Block Diagram

Additional Resources

Kit Contents

- USRP-2974

- 30 dB SMA Attenuator

- SMA Cable

- Power Supply

- Getting Started Guide

Quotes and Sales

Email:sales@tekdf.com

Wechat:dftech_info