您的购物车目前是空的!

标签: LimeSDR

-

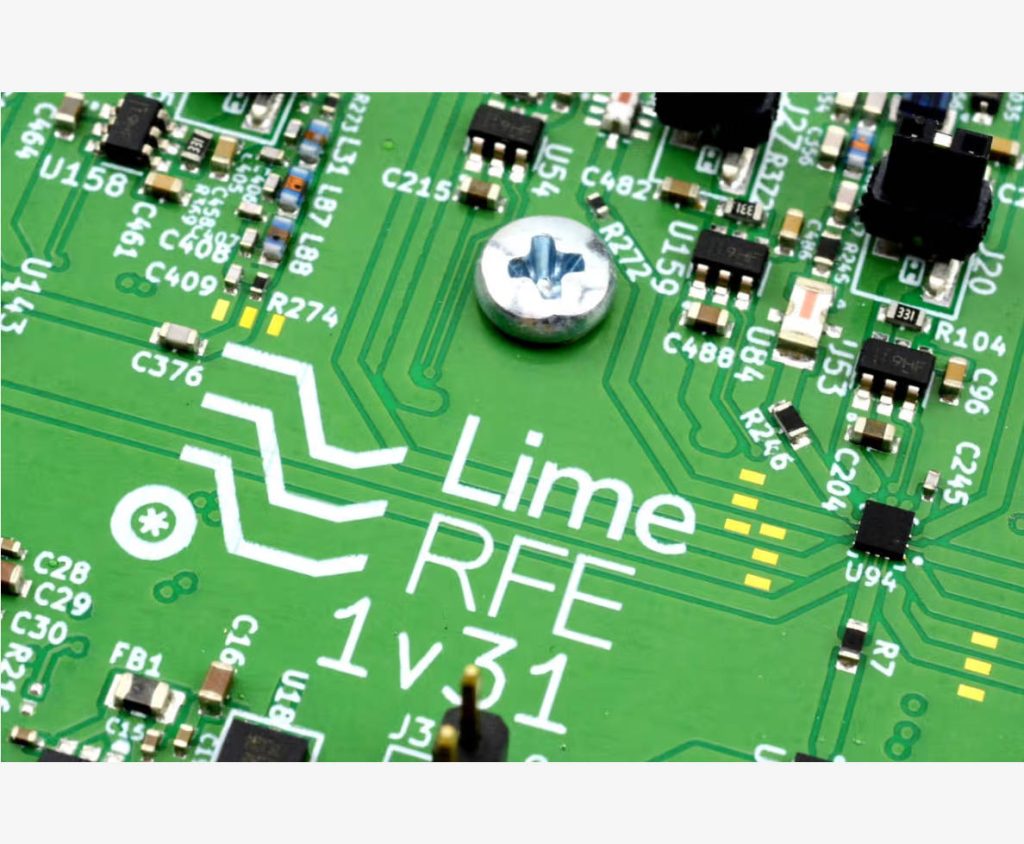

LimeRFE

简介

Lime RF Front-End (LimeRFE) 是一款开放式硬件射频前端模块,其支持电路可增强 LimeSDR 系列开发板和 LimeNET Micro,从而提供完整的解决方案,涵盖从业余无线电到符合标准的蜂窝网络等各种应用。

LimeRFE 将增强任何基于 SDR 的无线解决方案,提供以下优势:

- 发射时信号更强、更清晰

- 接收时噪音更低

- 覆盖范围更广

特征

适用于 LimeSDR 平台的软件可定义射频前端模块

单个 LimeRFE 可覆盖三种截然不同的频段:蜂窝、业余无线电和宽带。任何特定时间使用的具体频段均可通过软件选择。通过实现射频前端的软件可定义,LimeRFE 标志着软件定义无线电发展的下一步。

高度集成的解决方案,拥有丰富的便捷功能

LimeRFE 不仅提供发射和接收放大功能,还提供特定频段的滤波功能,并集成了用于蜂窝频段 FDD 操作的双工器。此外,它还提供功率和 VSWR(需要外部定向耦合器)测量功能,并且可以通过 USB 或直接连接到 LimeSDR 开发板进行配置。

规格

蜂窝

Band Duplex Downlink (MHz) Uplink (MHz) Modulated Power (dBm) Tx Gain (dB) Tx P1dB (dBm) Rx Gain (dB) Rx NF (dB) Rx IIP3 (dBm) 1 FDD 2110-2170 1920-1980 24 37 28 11 6.5 19 2 / PCS-1900 FDD 1930-1990 1850-1910 24 40 30.5 12 5.5 19.5 3 / DCS-1800 FDD 1805-1880 1710-1785 24 40 29.5 13 6 19 7 FDD 2620-2690 2500-2570 24 37 26 8 6 21 38 TDD 2570-2620 2570-2620 24 38 26 8 6 20 宽带

Band Freq (MHz) Min Tx Gain (dB) Max Tx Gain (dB) Min Tx P1dB (dBm) Max Tx P1dB (dBm) Min Rx Gain (db) Max Rx Gain (db) Min Rx NF (dB) Max Rx NF (dB) Min Rx IIP3 (dBm) Max Rx IIP3 (dBm) WB1000 1-1000 27 45 22.5 28.5 17 21.8 3.4 4.4 11.5 18 WB4000 1000-4000 12 33 14 24 7.8 18.4 2.7 5.5 10 23 业余无线电

Band Frequency (MHz) Tx Gain (dB) Tx P1dB (dBm) Rx Gain (dB) Rx NF (dB) Rx IIP3 (dBm) HAM 30 / HF* 1-5 38 33 21 / 0-14 HAM 30 / HF* 5-30 38 33 21 6 15 HAM 50-70 / 6m, 4m 50-54, 69.9-70.6 37 32 19 3.5 14 HAM 145 / 2m 144-146 31 34 18 3.7 12.6 HAM 220 / 1.25m 220-225 33 34 18 3.7 14.8 HAM 435 / 70cm 430-440 33 34 15 4 10 HAM 920 / 33cm 902-928 35 30 17 2.8 16 HAM 1280 / 23cm 1240-1325 31 31 16 2.8 20 HAM 2400 / 13cm 2300-2450 41 28.5 13 3.8 15.5 HAM 3500 / 9cm 3300-3500 33 25 7.5 4.5 12.5 滤波器

- 每个频段均有适合 RX 和 TX 的滤波

- 可选 AM/FM 陷波滤波器

开源

- 固件

- Lime Suite 集成(GUI 和 API)

射频功率和驻波比计

- 1-4000 MHz 射频功率和驻波比 (VSWR) 计(需外接定向耦合器)

- 蜂窝频段发射功率计(集成耦合器)

接口

- USB(通过 PC 控制)

- I2C(通过 SDR 控制)

- 4 个双向电平转换 GPIO:

- 1.2 – 5.5 V

- 每个 I/O 均配备高压大功率达林顿驱动级,用于驱动电感负载(例如同轴继电器)

- 可独立切换方向(输入/输出)

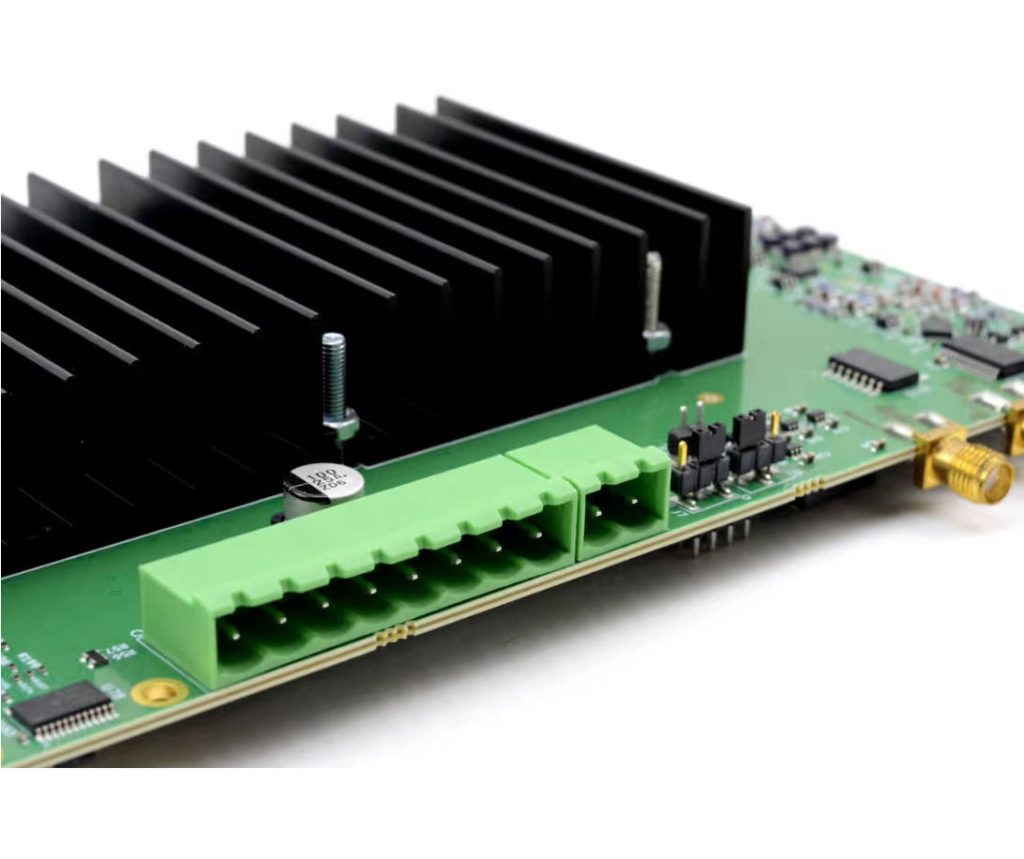

连接器

- SMA

- Micro USB

- 10 针接口 (SDR)

- 可插拔端子 (GPIO)

尺寸

- 16 x 15 x 4 厘米

电源

- 12VDC,通过管状插孔或3针接口

-

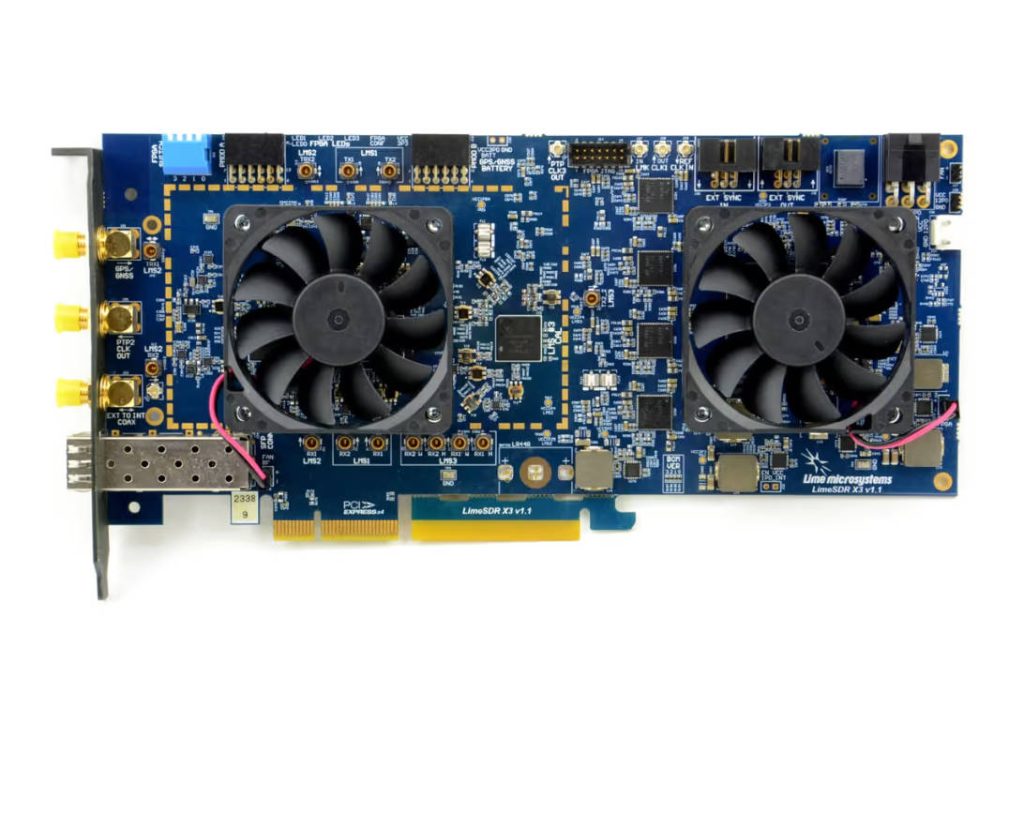

LimeSDR X3

简介

LimeSDR X3 是一款全尺寸 PCIe Gen 2 x4 卡,集成三个 Lime Microsystems LMS7002M 收发器,可同时支持 4G、5G 和自适应数字预失真 (ADPD),以实现功率放大器 (PA) 的线性化。LimeSDR X3 是用于 LimeNET 2.0 和 LimeNET Mini 2.0 等交钥匙系统的无线收发器平台。

LimeSDR X3 的设计充分考虑了蜂窝网络,但也可用于支持任何空中接口,并可用于数字视频广播 (DVB) 等应用。

LimeSDR X3 标配针对热门 4G 和 5G 频段优化的射频匹配网络,但可根据客户需求针对其他频段进行优化。

特征

面向高性能应用的先进无线电平台

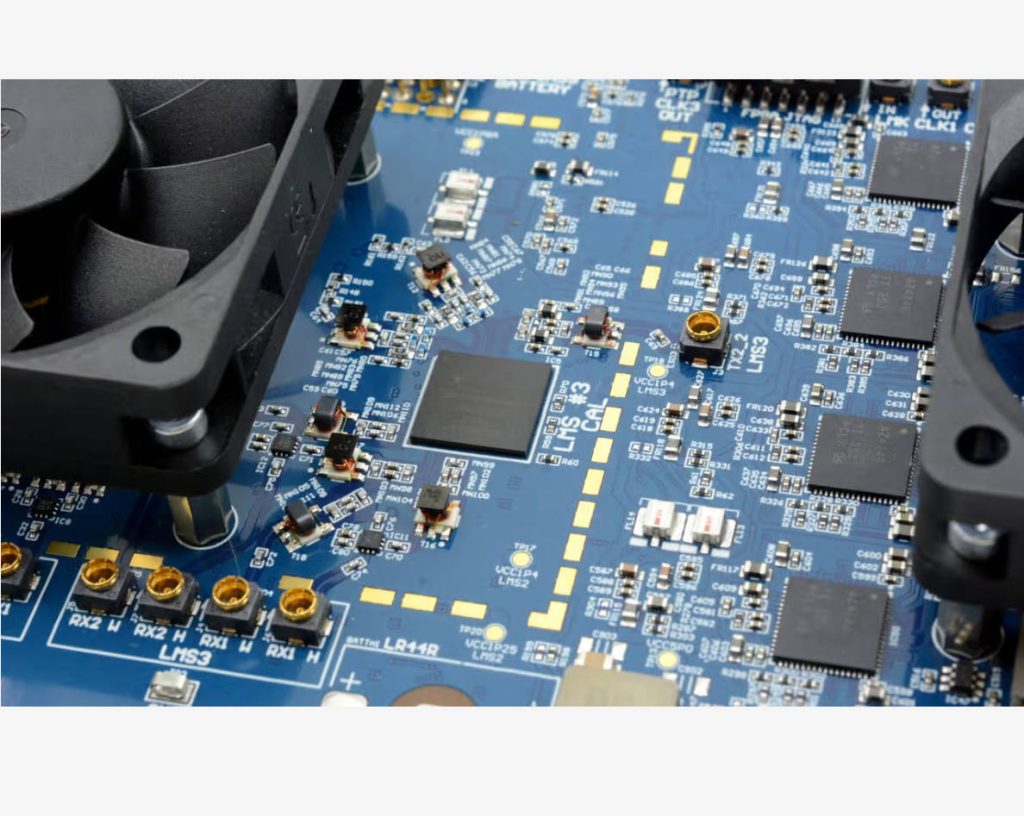

LimeSDR X3 采用 AMD Artix-7 FPGA,包含 215K 个逻辑单元和 740 个 DSP 芯片,以及三个 LMS7002M 收发器,这些收发器通常用于 4G、5G 和 ADPD。

5G 专用收发器采用高速 ADC 和 DAC,能够支持高达 100MHz 的射频带宽和 2×2 MIMO。电路板上的射频开关还可以将其连接到第三个收发器,该收发器旨在与 ADPD 配合使用并用于校准。

4G 和 5G 专用收发器的发射路径中均配备 PA 驱动器。

LimeSDR X3 是 Lime 自适应数字预失真 (LimeADPD) 的目标平台,LimeADPD 是一个完全开源的软件和 FPGA 网关实现,它不仅提供 ADPD,还提供波峰因数降低 (CFR) 以及用于 I/Q 不平衡校正和增益平坦化的均衡器。

白兔协议 (White Rabbit) 支持高精度时间和频率传输

LimeSDR X3 可配置为支持白兔精确时间协议 (WR PTP),从而提供高精度时间和频率传输,使应用程序能够扩展到数千个节点,网络元素之间的距离可达 10 公里。

白兔计时网络采用光纤介质,能够实现高精度同步,这得益于其结合使用 IEEE 1588 PTP 和同步以太网 (SyncE) 进行 L1 同步,以及相位测量进行链路延迟计算。这使得同步精度达到亚纳秒级,而 IEEE 1588-2008 的精度为亚微秒级。

LimeSDR X3 配备一个 SFP 笼,可与白兔协议配合使用(建议使用带有单个 LC 连接器的 1000BASE-BX10 标准双向收发器)。出于评估目的,如果只需要两个节点,可以将两块 LimeSDR X3 板直接连接,并将其中一块配置为 PTP 主控板。需要具有三个或更多节点的白兔交换机。

规格

射频收发器

- 1号 (4G):Lime Microsystems LMS7002M:

- 配置:MIMO(2xTX,2xRX)

- 频率范围:30 MHz – 3.8 GHz

- 带宽:120 MHz

- 采样深度:12 位

- 采样率:120 MSPS SISO / 90 MSPS MIMO

- 发射功率:最大 10 dBm(取决于频率)

- 2号 (5G):Lime Microsystems LMS7002M,带外部 ADC + DAC:

- 配置:MIMO(2xTX,2xRX)

- 频率范围:300 MHz – 3.8 GHz

- 带宽:100 MHz(平坦响应)

- 采样深度:14 位 ADC 和 16 位 DAC

- 采样率:高达 160 Msps ADC / 250 Msps DAC

- 发射功率:最大 10 dBm(取决于频率)

- 3(校准/ADPD):Lime Microsystems LMS7002M,带外部 ADC:

- 配置:MIMO(2xTX,2xRX)

- 频率范围:30 MHz – 3.8 GHz

- 带宽:120 MHz

- 采样深度:14 位 ADC / 12 位 DAC

- 采样率:高达 160 Msps ADC

- 发射功率:最大 10 dBm(取决于频率)

FPGA

Artix-7 XC7A200T:

- 676-FCBGA (27×27) 封装

- 215,360 个逻辑单元

- 740 个 DSP 逻辑单元

- 13 Mb 块 RAM

- x4 Gen 2 PCIe 接口

- 10 个时钟管理模块 (CMT),每个模块包含一个 MMCM 和一个 PLL

Flash 存储

- 256 Mbit FPGA配置闪存

EEPROM 存储

- 4x 128Kbit(16K x 8)EEPROM(用于每个RF收发器和FPGA数据)

其他设备

- 温度传感器

- 加密认证设备

- GNSS 接收器

时钟系统

- 30.72MHz(默认)VCOCXO 和 38.4MHz(可选)VCTCXO

- VCOCXO 同步选项:

- GNSS PPS 信号

- 参考时钟输入或板载 DAC

- White Rabbit PTP(从机或主机)

- 用于基带 DAC、ADC 的时钟发生器/PLL

GPIO

- 2 个 PMOD 接口(间距 0.1 英寸)连接至 FPGA

- 4 个双色 (RG) LED 连接至 FPGA

- 4 个开关连接至 FPGA

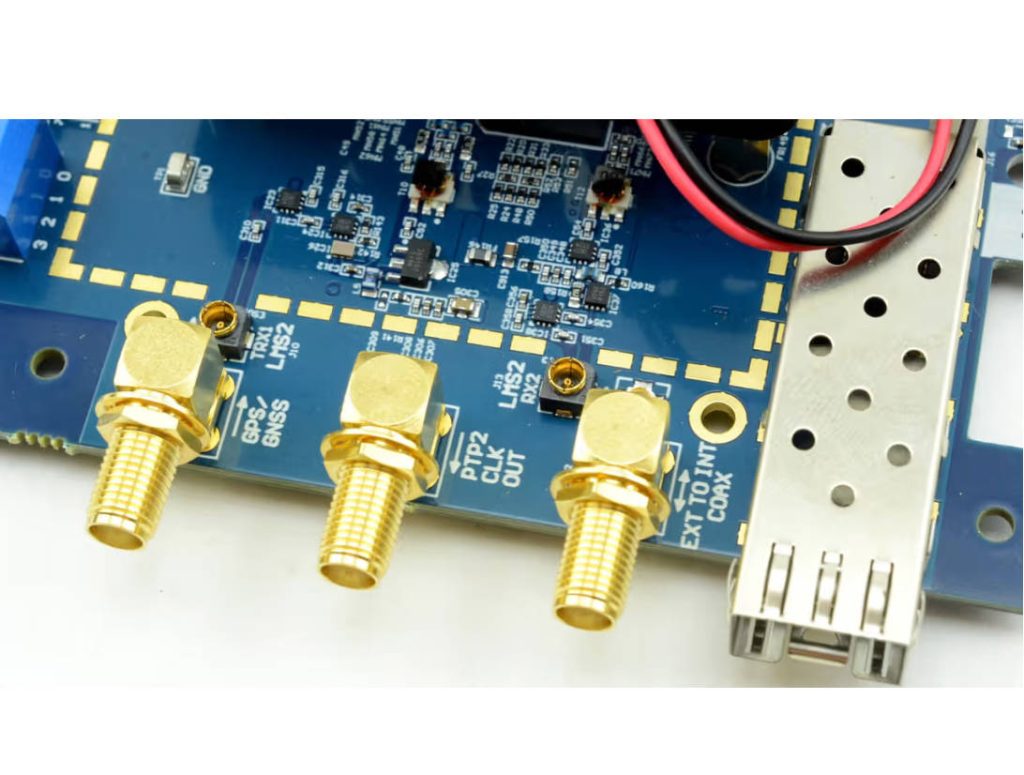

连接器

- 同轴射频 (SMA 和 uFL/MMCX) 连接器

- uFL/MMCX 连接器和接头,用于参考时钟输入/输出、GNSS 天线

- 12V 接头,用于为外部设备供电

- 风扇接头

- FPGA JTAG 连接器(2mm 间距)

尺寸

- 232.5mm x 106.7mm(9.15” x 4.2”)(不含连接器)

电源

- 12V 6针PCIe电源连接器

- 1号 (4G):Lime Microsystems LMS7002M: