您的购物车目前是空的!

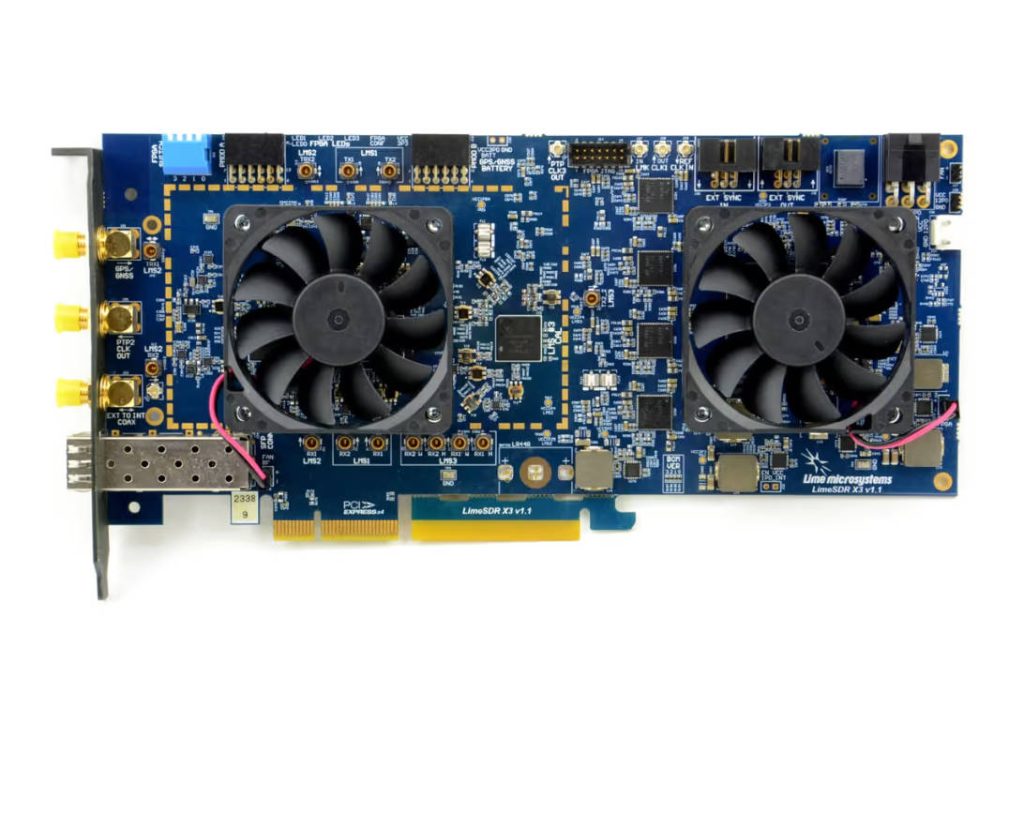

LimeSDR X3

简介

LimeSDR X3 是一款全尺寸 PCIe Gen 2 x4 卡,集成三个 Lime Microsystems LMS7002M 收发器,可同时支持 4G、5G 和自适应数字预失真 (ADPD),以实现功率放大器 (PA) 的线性化。LimeSDR X3 是用于 LimeNET 2.0 和 LimeNET Mini 2.0 等交钥匙系统的无线收发器平台。

LimeSDR X3 的设计充分考虑了蜂窝网络,但也可用于支持任何空中接口,并可用于数字视频广播 (DVB) 等应用。

LimeSDR X3 标配针对热门 4G 和 5G 频段优化的射频匹配网络,但可根据客户需求针对其他频段进行优化。

特征

面向高性能应用的先进无线电平台

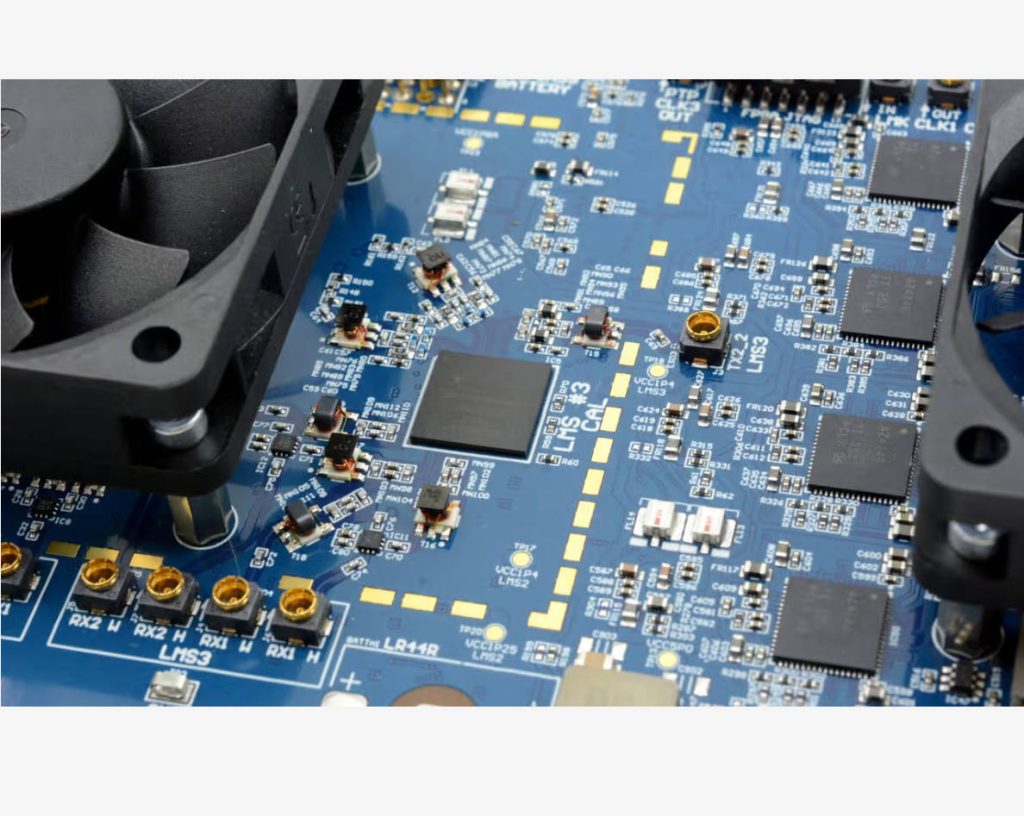

LimeSDR X3 采用 AMD Artix-7 FPGA,包含 215K 个逻辑单元和 740 个 DSP 芯片,以及三个 LMS7002M 收发器,这些收发器通常用于 4G、5G 和 ADPD。

5G 专用收发器采用高速 ADC 和 DAC,能够支持高达 100MHz 的射频带宽和 2×2 MIMO。电路板上的射频开关还可以将其连接到第三个收发器,该收发器旨在与 ADPD 配合使用并用于校准。

4G 和 5G 专用收发器的发射路径中均配备 PA 驱动器。

LimeSDR X3 是 Lime 自适应数字预失真 (LimeADPD) 的目标平台,LimeADPD 是一个完全开源的软件和 FPGA 网关实现,它不仅提供 ADPD,还提供波峰因数降低 (CFR) 以及用于 I/Q 不平衡校正和增益平坦化的均衡器。

白兔协议 (White Rabbit) 支持高精度时间和频率传输

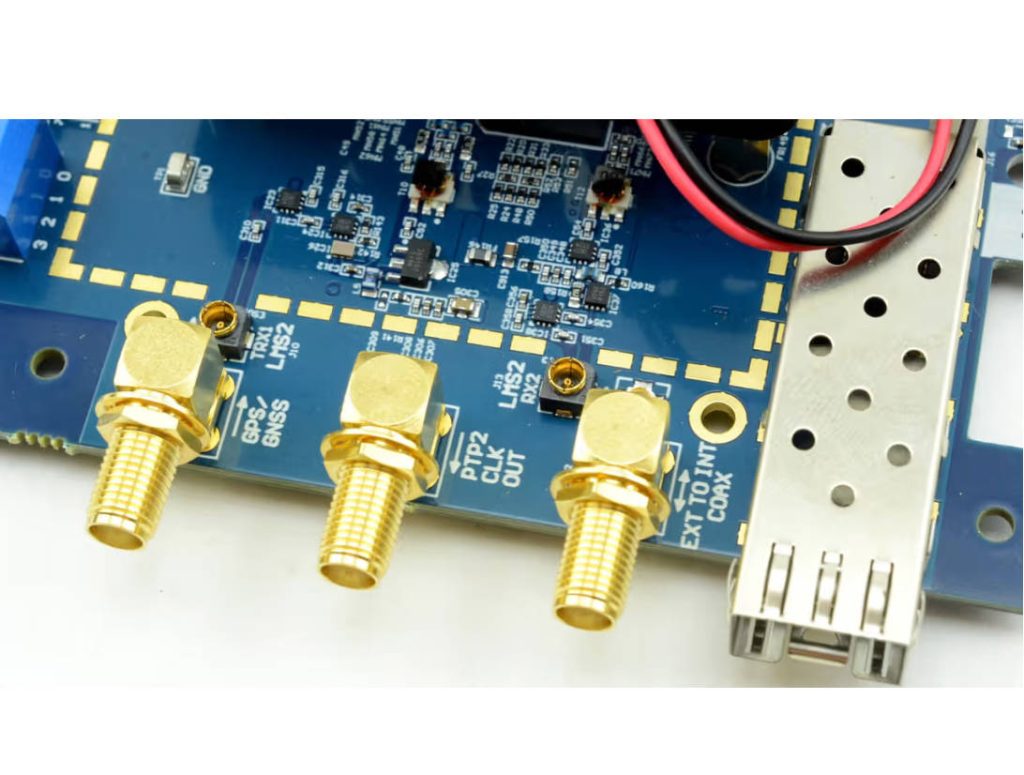

LimeSDR X3 可配置为支持白兔精确时间协议 (WR PTP),从而提供高精度时间和频率传输,使应用程序能够扩展到数千个节点,网络元素之间的距离可达 10 公里。

白兔计时网络采用光纤介质,能够实现高精度同步,这得益于其结合使用 IEEE 1588 PTP 和同步以太网 (SyncE) 进行 L1 同步,以及相位测量进行链路延迟计算。这使得同步精度达到亚纳秒级,而 IEEE 1588-2008 的精度为亚微秒级。

LimeSDR X3 配备一个 SFP 笼,可与白兔协议配合使用(建议使用带有单个 LC 连接器的 1000BASE-BX10 标准双向收发器)。出于评估目的,如果只需要两个节点,可以将两块 LimeSDR X3 板直接连接,并将其中一块配置为 PTP 主控板。需要具有三个或更多节点的白兔交换机。

规格

射频收发器

- 1号 (4G):Lime Microsystems LMS7002M:

- 配置:MIMO(2xTX,2xRX)

- 频率范围:30 MHz – 3.8 GHz

- 带宽:120 MHz

- 采样深度:12 位

- 采样率:120 MSPS SISO / 90 MSPS MIMO

- 发射功率:最大 10 dBm(取决于频率)

- 2号 (5G):Lime Microsystems LMS7002M,带外部 ADC + DAC:

- 配置:MIMO(2xTX,2xRX)

- 频率范围:300 MHz – 3.8 GHz

- 带宽:100 MHz(平坦响应)

- 采样深度:14 位 ADC 和 16 位 DAC

- 采样率:高达 160 Msps ADC / 250 Msps DAC

- 发射功率:最大 10 dBm(取决于频率)

- 3(校准/ADPD):Lime Microsystems LMS7002M,带外部 ADC:

- 配置:MIMO(2xTX,2xRX)

- 频率范围:30 MHz – 3.8 GHz

- 带宽:120 MHz

- 采样深度:14 位 ADC / 12 位 DAC

- 采样率:高达 160 Msps ADC

- 发射功率:最大 10 dBm(取决于频率)

FPGA

Artix-7 XC7A200T:

- 676-FCBGA (27×27) 封装

- 215,360 个逻辑单元

- 740 个 DSP 逻辑单元

- 13 Mb 块 RAM

- x4 Gen 2 PCIe 接口

- 10 个时钟管理模块 (CMT),每个模块包含一个 MMCM 和一个 PLL

Flash 存储

- 256 Mbit FPGA配置闪存

EEPROM 存储

- 4x 128Kbit(16K x 8)EEPROM(用于每个RF收发器和FPGA数据)

其他设备

- 温度传感器

- 加密认证设备

- GNSS 接收器

时钟系统

- 30.72MHz(默认)VCOCXO 和 38.4MHz(可选)VCTCXO

- VCOCXO 同步选项:

- GNSS PPS 信号

- 参考时钟输入或板载 DAC

- White Rabbit PTP(从机或主机)

- 用于基带 DAC、ADC 的时钟发生器/PLL

GPIO

- 2 个 PMOD 接口(间距 0.1 英寸)连接至 FPGA

- 4 个双色 (RG) LED 连接至 FPGA

- 4 个开关连接至 FPGA

连接器

- 同轴射频 (SMA 和 uFL/MMCX) 连接器

- uFL/MMCX 连接器和接头,用于参考时钟输入/输出、GNSS 天线

- 12V 接头,用于为外部设备供电

- 风扇接头

- FPGA JTAG 连接器(2mm 间距)

尺寸

- 232.5mm x 106.7mm(9.15” x 4.2”)(不含连接器)

电源

- 12V 6针PCIe电源连接器

发表回复

要发表评论,您必须先登录。